次世代の 800G コヒーレント DSP とアルゴリズムの調整に関するマーベルの見解には、消費電力の削減、シグナル インテグリティの改善、およびサイズの縮小という全体的な目標があります。 MOSFET ノードのプロセス規模を縮小し、精度を向上させることは、従来の最適化ルートです。

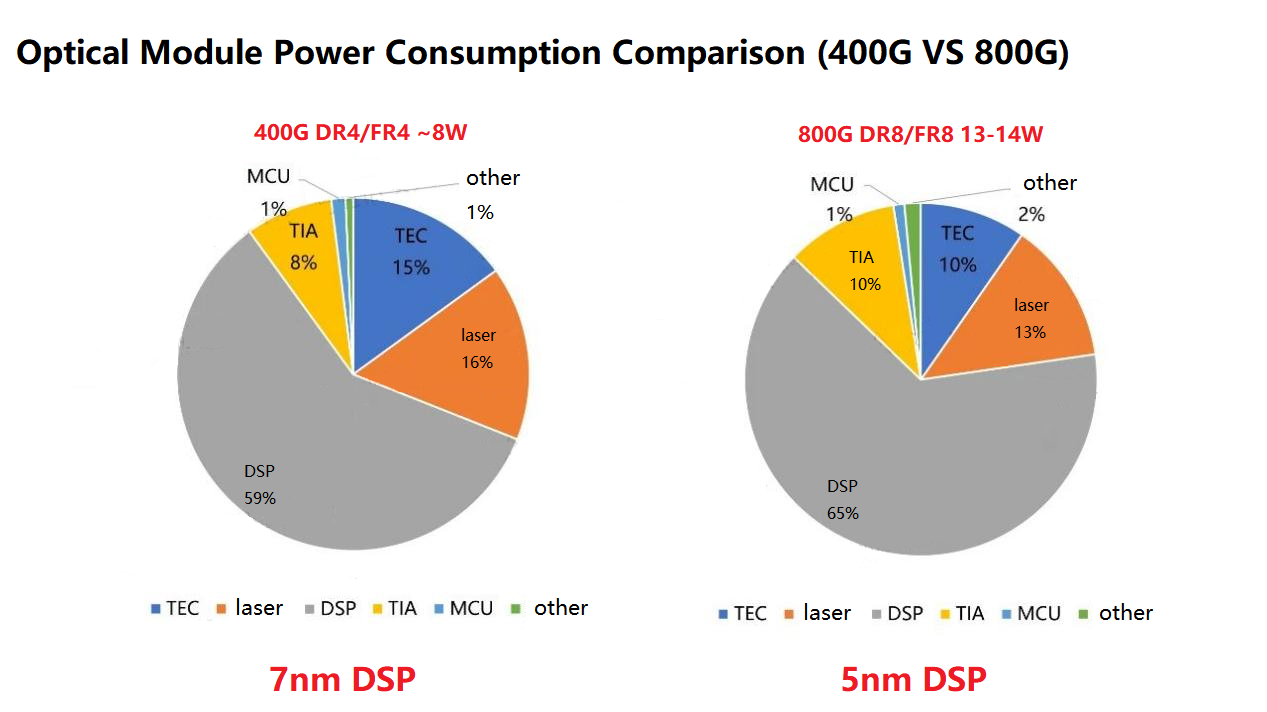

Marvell は、4 年に 400G PAM4 7nm ベースの DSP チップを発売し、今年の終わりにその上に更新されたバージョンを発売することで、PAM2020 DSP で支配的な地位を占めています。 先週、Marvell は 5nm 800G PAM4 DSP を発表しました。 800nm DSP を使用した 5G は、光モジュールで約 13 ~ 14W の電力を消費します。

Marvell は、 800G光モジュール 12W まで下げることができますが、TEC の動作温度は記載されていません。

シグナル インテグリティの点でもパフォーマンスが向上しています。 100 波 10G で 2km の伝送が可能であり、これは競争力があります。 10G の 800km ~ XNUMXkm の範囲では、業界は IM/DD を使用するか、コヒーレントを使用するかで引き裂かれた状態にありました。

PAM4 を使用する場合、以前のパフォーマンスでは不十分です。 コヒーレントを使用すると、価格が高くなり、実行が困難になり、消費電力が増加します。

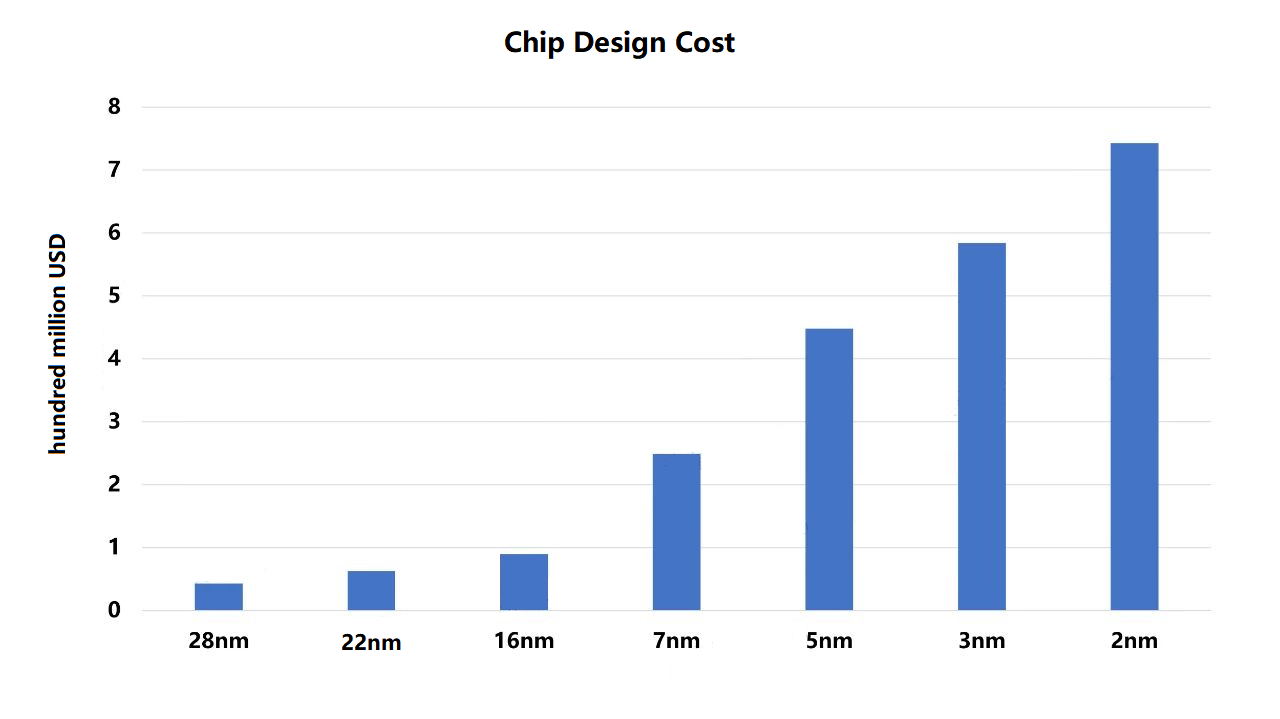

5nm チップの設計コストはますます高くなっています。 光モジュールが最初に DSP で始まったとき、10 年前のプロセス ノードは 65nm で、設計コストは 24 万ドルでした。 7 年にそれぞれが 2020nm ノードを発売するまでに、設計コストはすでに約 250 億 XNUMX 万ドルに達していました。 チップはお金を燃やすビジネスであり、資本クランプ技術に対する競争上の障壁です。

5nm チップ設計のコストは約 450 億 XNUMX 万ドルで、ヘッド効果はますます明白になっています。 市場シェアの小さいメーカーは、徐々に競争から撤退します。

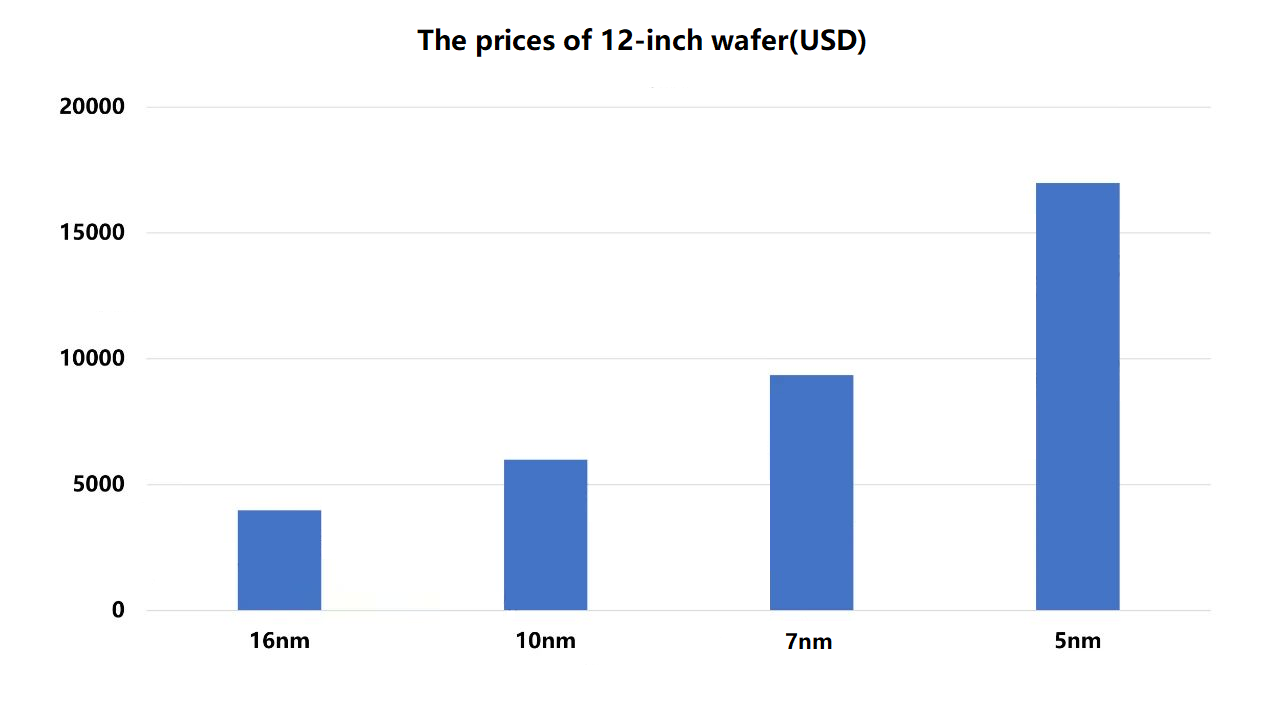

設計コストの上昇に加えて、OEM のコストも上昇しています。 市場規模の増加に伴い、設計コストが削減され、実際の材料費である鋳造所の価格が低下します。

12 インチ ウェーハ、65nm プロセス ノードのコストはわずか 2,000 ドルです。 7nm ファウンドリーの価格は 9300 ドルと高く、5nm ウェーハは 17,000 個あたり約 XNUMX ドルです。 チップは小さく、プロセスの価格は高くなります。 チップの平均価格が下がり続けるのは難しい。

5nmチップは、シングルチップの価格を追求するのではなく、ホットスワップ可能な光モジュールが1.6Tまで継続できるかどうかの重要な数値を満たすために、少し低消費電力を追求するのは良いことです.

関連製品:

-

QSFP-DD-800G-DR8D QSFP-DD 8x100G DR PAM4 1310nm 500m DOM デュアル MPO-12 SMF 光トランシーバー モジュール

$1250.00

QSFP-DD-800G-DR8D QSFP-DD 8x100G DR PAM4 1310nm 500m DOM デュアル MPO-12 SMF 光トランシーバー モジュール

$1250.00

-

OSFP-800G-FR8L OSFP 800G FR8 PAM4 CWDM8 デュプレックス LC 2km SMF 光トランシーバー モジュール

$3000.00

OSFP-800G-FR8L OSFP 800G FR8 PAM4 CWDM8 デュプレックス LC 2km SMF 光トランシーバー モジュール

$3000.00

-

OSFP-800G-2LR4L OSFP 2x400G LR4 PAM4 CWDM4 二重二重 LC 10km SMF 光トランシーバー モジュール

$2000.00

OSFP-800G-2LR4L OSFP 2x400G LR4 PAM4 CWDM4 二重二重 LC 10km SMF 光トランシーバー モジュール

$2000.00

-

OSFP-800G-LR8D OSFP 8x100G LR PAM4 1310nm デュアル MPO-12 10km SMF 光トランシーバー モジュール

$1800.00

OSFP-800G-LR8D OSFP 8x100G LR PAM4 1310nm デュアル MPO-12 10km SMF 光トランシーバー モジュール

$1800.00

-

OSFP-800G-LR8 OSFP 8x100G LR PAM4 1310nm MPO-16 10km SMF 光トランシーバー モジュール

$1800.00

OSFP-800G-LR8 OSFP 8x100G LR PAM4 1310nm MPO-16 10km SMF 光トランシーバー モジュール

$1800.00

-

OSFP-800G-FR8D OSFP 8x100G FR PAM4 1310nm デュアル MPO-12 2km SMF 光トランシーバー モジュール

$1100.00

OSFP-800G-FR8D OSFP 8x100G FR PAM4 1310nm デュアル MPO-12 2km SMF 光トランシーバー モジュール

$1100.00

-

OSFP-800G-SR8D OSFP 8x100G SR8 PAM4 850nm 100m DOM デュアル MPO-12 MMF 光トランシーバー モジュール

$650.00

OSFP-800G-SR8D OSFP 8x100G SR8 PAM4 850nm 100m DOM デュアル MPO-12 MMF 光トランシーバー モジュール

$650.00

-

OSFP-800G-SR8 OSFP 8x100G SR8 PAM4 850nm MTP/MPO-16 100m OM4 MMF FEC 光トランシーバー モジュール

$650.00

OSFP-800G-SR8 OSFP 8x100G SR8 PAM4 850nm MTP/MPO-16 100m OM4 MMF FEC 光トランシーバー モジュール

$650.00

-

QSFP-DD-800G-FR8L QSFP-DD 800G FR8 PAM4 CWDM8 2km DOM デュプレックス LC SMF 光トランシーバー モジュール

$3000.00

QSFP-DD-800G-FR8L QSFP-DD 800G FR8 PAM4 CWDM8 2km DOM デュプレックス LC SMF 光トランシーバー モジュール

$3000.00

-

QSFP-DD-800G-2LR4 QSFP-DD 2x400G LR4 PAM4 CWDM4 10km デュアル CS SMF FEC 光トランシーバー モジュール

$2100.00

QSFP-DD-800G-2LR4 QSFP-DD 2x400G LR4 PAM4 CWDM4 10km デュアル CS SMF FEC 光トランシーバー モジュール

$2100.00

-

QSFP-DD-800G-2FR4L QSFP-DD 2x400G FR4 PAM4 CWDM4 2km DOM 二重二重 LC SMF 光トランシーバー モジュール

$1800.00

QSFP-DD-800G-2FR4L QSFP-DD 2x400G FR4 PAM4 CWDM4 2km DOM 二重二重 LC SMF 光トランシーバー モジュール

$1800.00

-

QSFP-DD-800G-LR8D QSFP-DD 8x100G LR PAM4 1310nm 10km デュアル MPO-12 SMF FEC 光トランシーバー モジュール

$1550.00

QSFP-DD-800G-LR8D QSFP-DD 8x100G LR PAM4 1310nm 10km デュアル MPO-12 SMF FEC 光トランシーバー モジュール

$1550.00

-

QSFP-DD-800G-LR8 QSFP-DD 8x100G LR PAM4 1310nm 10km MPO-16 SMF FEC 光トランシーバー モジュール

$1600.00

QSFP-DD-800G-LR8 QSFP-DD 8x100G LR PAM4 1310nm 10km MPO-16 SMF FEC 光トランシーバー モジュール

$1600.00

-

QSFP-DD-800G-FR8D QSFP-DD 8x100G FR/DR8+ PAM4 1310nm 2km DOM デュアル MPO-12 SMF 光トランシーバー モジュール

$1450.00

QSFP-DD-800G-FR8D QSFP-DD 8x100G FR/DR8+ PAM4 1310nm 2km DOM デュアル MPO-12 SMF 光トランシーバー モジュール

$1450.00

-

OSFP-800G-2FR4 OSFP 2x400G FR4 PAM4 CWDM4 2km DOM デュアル CS SMF 光トランシーバー モジュール

$1500.00

OSFP-800G-2FR4 OSFP 2x400G FR4 PAM4 CWDM4 2km DOM デュアル CS SMF 光トランシーバー モジュール

$1500.00

-

QSFP-DD-800G-SR8 800G SR8 QSFP-DD 850nm 100m OM4 MMF MPO-16 光トランシーバー モジュール

$850.00

QSFP-DD-800G-SR8 800G SR8 QSFP-DD 850nm 100m OM4 MMF MPO-16 光トランシーバー モジュール

$850.00

-

OSFP-800G-2FR4L OSFP 2x400G FR4 PAM4 1310nm 2km DOM デュアルデュプレックス LC SMF 光トランシーバ モジュール

$1200.00

OSFP-800G-2FR4L OSFP 2x400G FR4 PAM4 1310nm 2km DOM デュアルデュプレックス LC SMF 光トランシーバ モジュール

$1200.00

-

QSFP-DD-800G-2FR4 800G QSFP-DD 2FR4 PAM4 1310nm 2km DOM デュアル CS SMF 光トランシーバー モジュール

$1900.00

QSFP-DD-800G-2FR4 800G QSFP-DD 2FR4 PAM4 1310nm 2km DOM デュアル CS SMF 光トランシーバー モジュール

$1900.00

-

QSFP-DD-800G-DR8 800G-DR8 QSFP-DD PAM4 1310nm 500m DOM MTP/MPO-16 SMF 光トランシーバー モジュール

$1300.00

QSFP-DD-800G-DR8 800G-DR8 QSFP-DD PAM4 1310nm 500m DOM MTP/MPO-16 SMF 光トランシーバー モジュール

$1300.00

-

OSFP-800G-DR8D 800G-DR8 OSFP PAM4 1310nm 500m DOM デュアル MTP/MPO-12 SMF 光トランシーバー モジュール

$850.00

OSFP-800G-DR8D 800G-DR8 OSFP PAM4 1310nm 500m DOM デュアル MTP/MPO-12 SMF 光トランシーバー モジュール

$850.00