Table of Contents

ToggleOverview

800G Ethernet is a high-bandwidth Ethernet standard that can transmit data rates of 800 Gbps (gigabits per second). It represents the latest advancement in Ethernet technology and is designed to meet the increasing demand for data transmission and the ability to handle large amounts of data.

The 25G and 50G Ethernet Consortium standards provide an 800G implementation specification based on 8 lanex100Gb/s technology, enabling adopters to deploy advanced high-bandwidth interoperable Ethernet technology.

800G Ethernet is mainly used for large data centers, cloud service environments, and applications that require high bandwidth. For these scenarios, it can provide higher speed, greater throughput, and better network performance, thus supporting faster and more efficient data communication.

Architecture

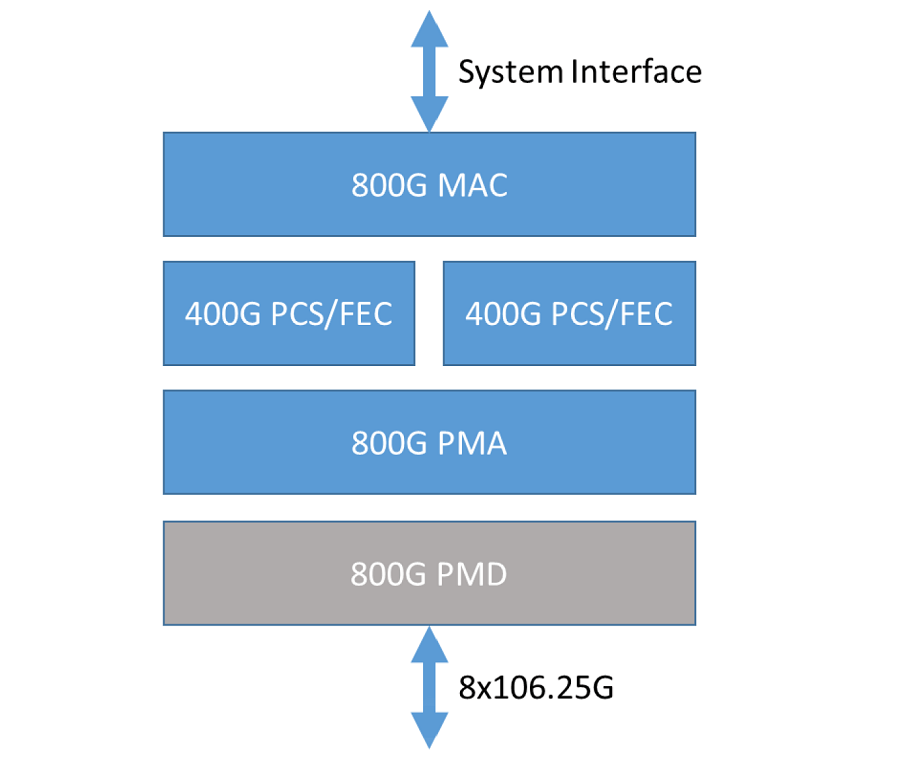

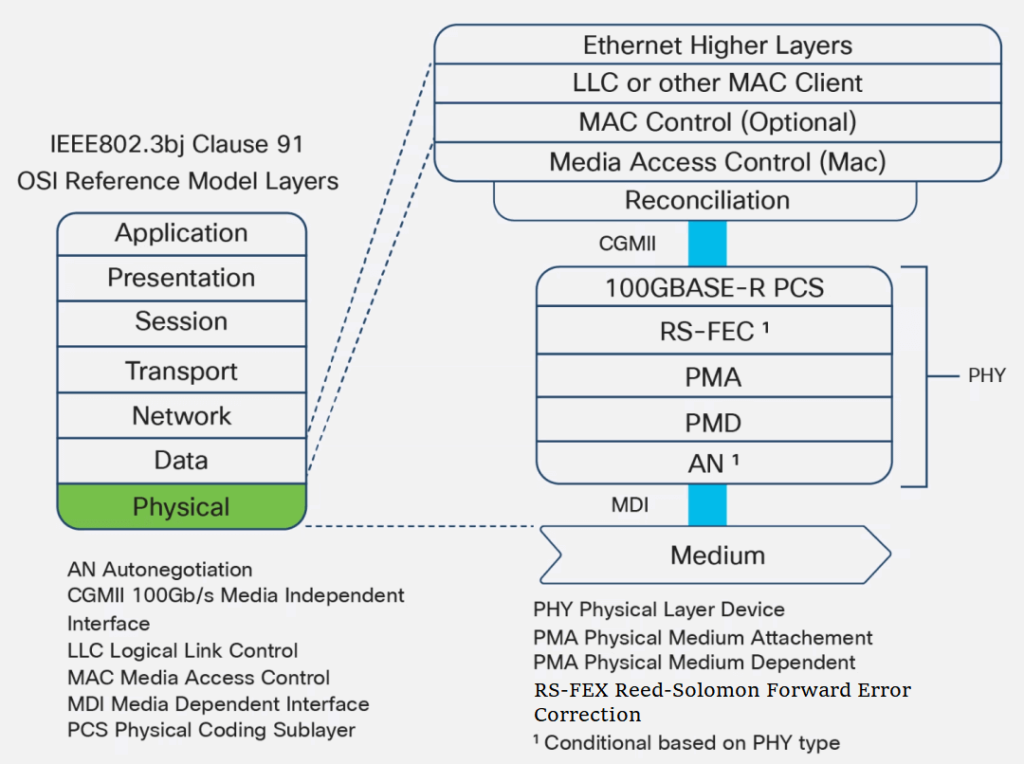

800Gb/s Ethernet technology is designed as an interface that uses eight 106 Gb/s lanes using 2xClause 119 PCSs (400G) to connect a single MAC operating at 800 Gb/s (though the 400G PCSs are modified, this is just a very high-level conceptual view). The following figure shows the high-level architecture.

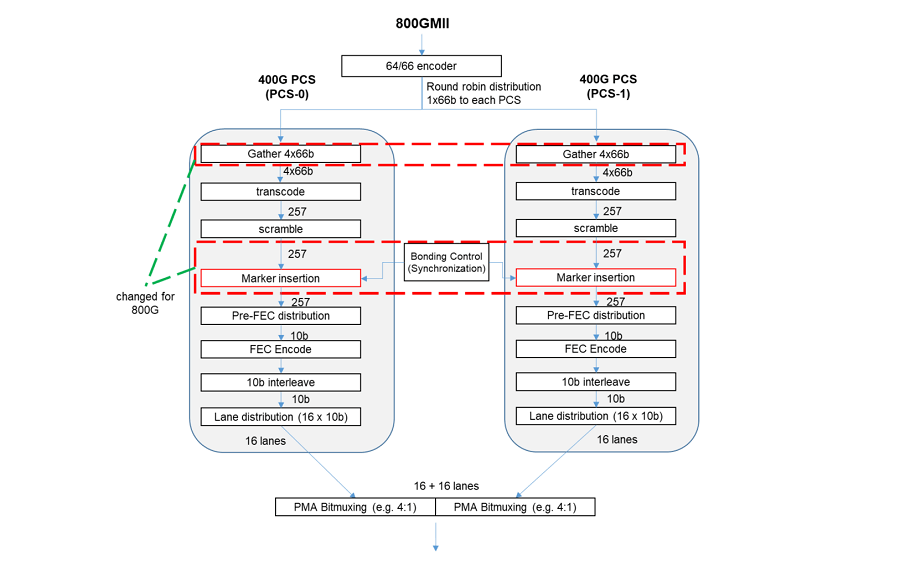

In the specific implementation process, the 800GBASE-R specification is not simply splicing two 400Gs together but introduces a new Media Access Control (MAC) and Physical Coding Sublayer (PCS) that can achieve 800G with minimal cost. Since the new PCS contains a reuse of the previous PCS, it retains the standard RS (544, 514) forward error correction and provides good backward compatibility features.

PCS/FEC

By utilizing two 400 Gb/s PCSs (including FEC) and supporting 32 PCS lanes (each lane speed is 25Gb/s) to support 800 Gb/s capability. The figure below shows the TX PCS data flow and functionality. 2×16 PCS lanes are generated from two PCS stacks, and then 4:1 bit multiplexing is performed by the PMA to the PMD to create 8x106G PMD lanes.

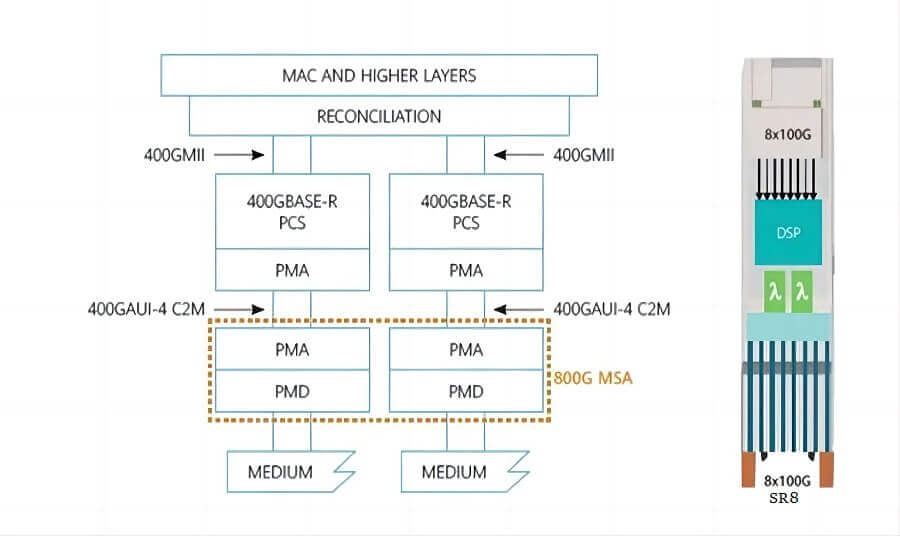

The figure below is a schematic diagram given by the 800G Pluggable MSA working group in the “800G MSA White Paper”, an 800G implementation scheme that can be quickly launched. By readjusting two 400G PMAs, an 800G PMA is obtained, a low-cost 800G PMD is defined, and an 800G Ethernet based on 8-channel 100Gb/s technology is realized.

Applications of 800G Ethernet

800G Ethernet is transforming industries by supporting data-intensive applications, including:

- AI and Machine Learning: Connects GPU clusters for training large-scale models, reducing latency and accelerating data processing.

- Cloud Computing: Enhances hyperscale data centers with higher throughput, supporting platforms like AWS and Azure.

- Ultra-High-Density Storage: Enables rapid data transfer for big data analytics and IoT applications.

- 5G and Edge Computing: Provides the bandwidth for high-speed mobile networks and edge data processing, driving smart cities and intelligent transportation.

- Telecommunications: Supports higher customer loads, ensuring reliable connectivity.

Technical Foundations of 800G Ethernet

800G Ethernet achieves its remarkable speed through an advanced architecture leveraging eight 106.25 Gbps lanes, doubling the capacity of 400G Ethernet. Key technical components include:

Media Access Control (MAC) and Physical Coding Sublayer (PCS)

The 800G Ethernet specification reuses two modified 400G PCSs (based on IEEE 802.3bs) to manage eight 100G lanes, resulting in 32 PCS lanes with RS(544,514) Forward Error Correction (FEC). This ensures low error rates and compatibility with existing standards, making 800G Ethernet cost-effective and interoperable.

Multi-Lane Distribution (MLD)

Data is distributed across 32 virtual lanes using unique alignment markers (AMs) inserted every 163,840 x 257b blocks. This ensures synchronization and prevents misalignment when interfacing with 400G ports, enhancing network reliability.

Chip-to-Module (C2M) and Chip-to-Chip (C2C) Interfaces

Governed by the IEEE 802.3ck standard, these interfaces operate at 106.25 Gbps per lane, supporting high-speed data transmission with minimal signal loss. This is critical for maintaining performance in high-density environments.

Optical Modules

800G Ethernet relies on advanced transceivers like QSFP-DD800 and OSFP, designed for low power consumption and high signal integrity. For example, FiberMall’s 800G QSFP-DD modules support up to 50 meters over multimode fiber (MMF) with MTP/MPO-16 connectors, ideal for data center applications.

800G Ethernet Standards and Development

Standardization ensures 800G Ethernet’s interoperability and adoption. Key milestones include:

2020: The Ethernet Technology Consortium (ETC) introduced the 800GBASE-R specification, leveraging 400G logic for a cost-effective 800G MAC and PCS.

2022: The first 51.2T switch chips were released, supporting 64 ports at 800 Gbps, enabling hardware implementation.

2023: The IEEE 802.3df standard defined physical layer specifications for 800G Ethernet, with the Optical Internetworking Forum (OIF) releasing 224 Gb/s standards for 800G and 1.6T systems.

Future Outlook: Over the next two years, standards will evolve to support 1.6T Ethernet and 200G-per-lane signaling, paving the way for even faster networks.

Challenges

The current 800G Ethernet implementation uses 8 channels, each channel transmission rate is 100Gbps. This doubles the PAM4 (four-level modulation) speed from the previous generation of 50Gbps to 100Gbps. The next-generation 800G transceiver under development will make the rate of each channel reach 200Gbps, which brings significant challenges because it requires both higher-order modulation and PAM4 data rates to be increased.

High-speed SerDes and power consumption

To support the increase of the overall bandwidth of the switch chip, the speed and power of SerDes are also increasing. Currently, the SerDes speed has increased from 10Gbit/s to 112Gbit/s. However, SerDes power consumption has become important to the system’s total power consumption. The next-generation switch chip will double the bandwidth again because the 102.4T switch will have 512 200 Gb/s SerDes channels. These silicon switches will support 800G and 1.6T on 224 Gb/s channels.

Solution:

Higher-speed SerDes: Research and develop higher-speed SerDes technology to meet the growing data transmission demand. This includes increasing the speed, reducing the power consumption, and improving the signal integrity of SerDes. Power consumption optimization: Adopt a power consumption optimization design method to reduce the power consumption of SerDes. This includes using advanced CMOS processes and low-power circuit design.

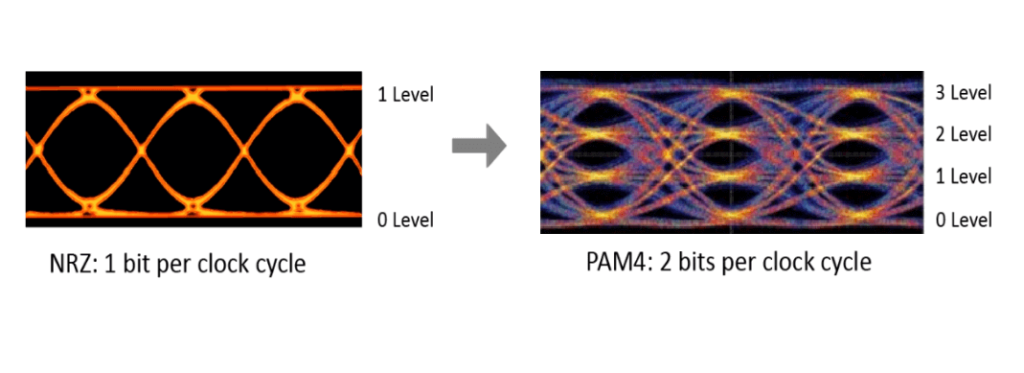

Pulse Amplitude Modulation

The current phase of 800G Ethernet employs a higher-order modulation technique that uses PAM4 (4-Level Pulse Amplitude Modulation) to transmit data so that each symbol carries multiple bits of information, thereby increasing the data transmission rate.

Higher-order modulation increases the number of bits per symbol and provides a trade-off between channel bandwidth and signal amplitude. PAM4 modulation is backward compatible with previous generations of products. It offers a better signal-to-noise ratio (SNR) compared to higher modulation schemes, thus reducing the overhead of forward error correction (FEC) that causes latency.

Solutions:

Better analog front-end (AFE): Research and develop higher-performance analog front-ends to support higher-order modulation schemes. This may include more accurate clock recovery, lower jitter, and better signal processing capabilities. Advanced equalization techniques: Use innovative digital signal processing (DSP) and equalization techniques to overcome distortion and noise in the channel. This helps improve the reliability of PAM4 signals. Explore higher modulation schemes: Although PAM4 is widely used in the current 800G Ethernet, future standards may adopt higher-order modulation schemes, such as PAM6 or PAM8. This will increase the transmission rate per symbol and bring higher complexity.

Overcoming 800G Ethernet Design Challenges

Implementing 800G Ethernet presents challenges that require innovative solutions:

Signal Integrity

High-speed signals face attenuation and crosstalk. Advanced equalization techniques like Decision Feedback Equalization (DFE) and Feed-Forward Equalization (FFE), combined with optimized PCB design, ensure reliable performance.

Power Consumption

800G Ethernet requires more power than previous standards. Energy-efficient components, power gating, and advanced cooling solutions, like those in FiberMall’s 800G switches, mitigate this issue.

Infrastructure Compatibility

Backward compatibility with 200G/400G networks is critical. Reusing 400G PCS logic and standards like QSFP-DD800 ensures seamless integration.

Cost

High initial costs can be a barrier. Standardized components and economies of scale, as offered by FiberMall, reduce expenses while maintaining performance.

How to reduce the bit error rate (BER) of 800G Ethernet?

In high-speed data transmission, the signal is affected by various interference and attenuation factors when passing through the channel. These include signal attenuation, noise, crosstalk, and other signal distortion factors. These factors cause bit errors in the signal, i.e., BER. In data transmission, the presence of BER may cause serious data corruption, reducing the availability and integrity of data. In previous high-speed data standards, such as 100G Ethernet, conventional fine-tuning equalizers and signal processing techniques were sufficient to reduce BER. However, in the higher-speed 800G Ethernet, more complex methods are needed to cope with the higher BER challenges. Forward error correction (FEC) is widely used to reduce BER. It involves adding redundant information in data transmission to help the receiver detect and correct transmission errors. FEC algorithms add redundant bits in data frames, enabling the receiver to reconstruct lost or damaged data bits. This helps improve the reliability of data transmission, especially in high-speed networks.

In the later development stages, such as 200Gb/s systems, more complex FEC algorithms are needed to cope with the higher BER challenges. These algorithms may include using more redundant data and more sophisticated error correction mechanisms to ensure the reliability of data transmission.

How to improve the energy efficiency of 800G Ethernet?

Improving the energy efficiency of 800G Ethernet is an important challenge, especially in large-scale data centers. Although the optical module design has become more efficient, reducing the power consumption per bit, the overall power consumption of the modules is still a serious issue, as large data centers usually have tens of thousands of optical modules. One way to solve the power consumption challenge of optical modules is to use co-packaged optical devices. This technology integrates the optoelectronic conversion function within the package of the optical module, reducing the power consumption of each module. Co-packaged optical devices can provide various advantages, including higher energy efficiency and smaller package sizes.

What are the benefits of 800G Ethernet?

- Increased bandwidth and data speed: With the rapid development of technologies such as big data, artificial intelligence, cloud services, etc., data traffic is constantly increasing. Most importantly, 800G Ethernet can handle more data streams and network connections simultaneously. In addition, 800G Ethernet achieves faster data upload, download, and transmission, improving data processing efficiency and user experience. With the increase in bandwidth and data speed, 800G Ethernet supports high-density and large-scale data transmission, while ensuring the stable and efficient operation of the network.

- High-performance computing field: In high-performance computing applications, such as scientific computing and artificial intelligence training, high-speed data transmission and processing capabilities are required. 800G network improves data transmission speed and higher network performance, to maintain the operation of high-performance computing tasks. This is very important for applications that handle large-scale complex calculations, such as scientific research, big data analysis, and artificial intelligence training. Introducing 800G Ethernet will further promote the innovation and development of the high-performance computing field.

- Support large-scale data centers: Data centers are key places for storing and processing large amounts of data. The emergence of 800G Ethernet technology can significantly improve the performance of data centers, accelerate data transmission speed and processing capabilities, and provide higher throughput and lower latency for data centers. In summary, 800G Ethernet plays an extremely important role in the current network environment, representing the future development trend of network technology.

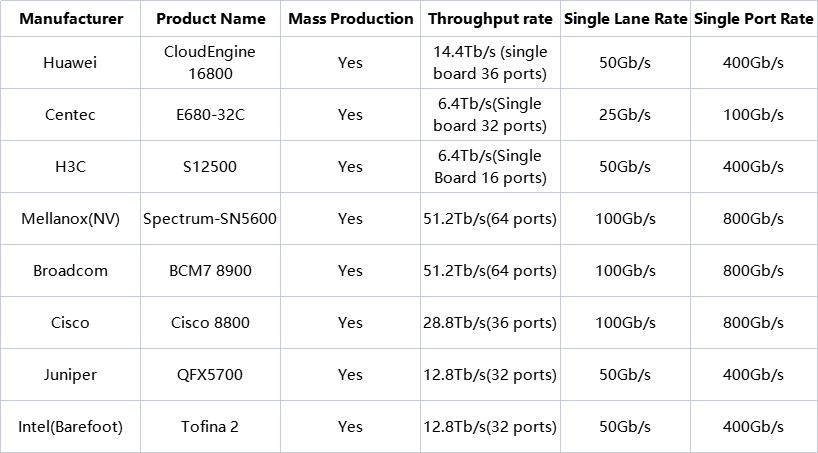

The current status of 400G/800G Ethernet products

Note: The data in the table above mainly comes from the product introduction pages of various manufacturers’ official websites (December 2023).

800G Ethernet is revolutionizing high-speed networking, offering unmatched bandwidth, scalability, and efficiency for data centers, AI, and 5G applications. As standards like IEEE 802.3df mature and hardware becomes more accessible, 800G Ethernet will drive digital transformation across industries. Contact FiberMall today to explore our cutting-edge 800G optical modules and switches, and build a future-ready network tailored to your needs.

Related Products:

-

QSFP-DD-800G-DR8D QSFP-DD 8x100G DR PAM4 1310nm 500m DOM Dual MPO-12 SMF Optical Transceiver Module

$1250.00

QSFP-DD-800G-DR8D QSFP-DD 8x100G DR PAM4 1310nm 500m DOM Dual MPO-12 SMF Optical Transceiver Module

$1250.00

-

QSFP-DD-800G-FR8L QSFP-DD 800G FR8 PAM4 CWDM8 2km DOM Duplex LC SMF Optical Transceiver Module

$3000.00

QSFP-DD-800G-FR8L QSFP-DD 800G FR8 PAM4 CWDM8 2km DOM Duplex LC SMF Optical Transceiver Module

$3000.00

-

QSFP-DD-800G-SR8 800G SR8 QSFP-DD 850nm 100m OM4 MMF MPO-16 Optical Transceiver Module

$850.00

QSFP-DD-800G-SR8 800G SR8 QSFP-DD 850nm 100m OM4 MMF MPO-16 Optical Transceiver Module

$850.00

-

QSFP-DD-800G-DR8 800G-DR8 QSFP-DD PAM4 1310nm 500m DOM MTP/MPO-16 SMF Optical Transceiver Module

$1300.00

QSFP-DD-800G-DR8 800G-DR8 QSFP-DD PAM4 1310nm 500m DOM MTP/MPO-16 SMF Optical Transceiver Module

$1300.00

-

OSFP-800G-DR8D-FLT 800G-DR8 OSFP Flat Top PAM4 1310nm 500m DOM Dual MTP/MPO-12 SMF Optical Transceiver Module

$1199.00

OSFP-800G-DR8D-FLT 800G-DR8 OSFP Flat Top PAM4 1310nm 500m DOM Dual MTP/MPO-12 SMF Optical Transceiver Module

$1199.00

-

OSFP-800G-SR8D-FLT OSFP 8x100G SR8 Flat Top PAM4 850nm 100m DOM Dual MPO-12 MMF Optical Transceiver Module

$650.00

OSFP-800G-SR8D-FLT OSFP 8x100G SR8 Flat Top PAM4 850nm 100m DOM Dual MPO-12 MMF Optical Transceiver Module

$650.00

-

OSFP-800G-SR8D OSFP 8x100G SR8 PAM4 850nm 100m DOM Dual MPO-12 MMF Optical Transceiver Module

$650.00

OSFP-800G-SR8D OSFP 8x100G SR8 PAM4 850nm 100m DOM Dual MPO-12 MMF Optical Transceiver Module

$650.00

-

OSFP-800G-DR8D 800G-DR8 OSFP PAM4 1310nm 500m DOM Dual MTP/MPO-12 SMF Optical Transceiver Module

$850.00

OSFP-800G-DR8D 800G-DR8 OSFP PAM4 1310nm 500m DOM Dual MTP/MPO-12 SMF Optical Transceiver Module

$850.00

-

QSFP-DD-800G-FR4 800G QSFP-DD800 FR4 (200G per line) PAM4 CWDM 2km DOM Duplex LC SMF Optical Transceiver Module

$3500.00

QSFP-DD-800G-FR4 800G QSFP-DD800 FR4 (200G per line) PAM4 CWDM 2km DOM Duplex LC SMF Optical Transceiver Module

$3500.00

-

QSFP-DD-800G-DR4 800G QSFP-DD800 DR4 (200G per line) 1311nm 500m Dual MPO-12 SMF Transceivers

$2850.00

QSFP-DD-800G-DR4 800G QSFP-DD800 DR4 (200G per line) 1311nm 500m Dual MPO-12 SMF Transceivers

$2850.00

-

OSFP-800G-2FR2L 800G OSFP 2FR2 (200G per line) PAM4 1291/1311nm 2km DOM Duplex LC SMF Optical Transceiver Module

$3000.00

OSFP-800G-2FR2L 800G OSFP 2FR2 (200G per line) PAM4 1291/1311nm 2km DOM Duplex LC SMF Optical Transceiver Module

$3000.00

-

OSFP-800G-DR4 800G OSFP DR4 (200G per line) PAM4 1311nm MPO-12 500m SMF DDM Optical Transceiver Module

$3000.00

OSFP-800G-DR4 800G OSFP DR4 (200G per line) PAM4 1311nm MPO-12 500m SMF DDM Optical Transceiver Module

$3000.00